歡迎來到實佳電子-線路板制造!

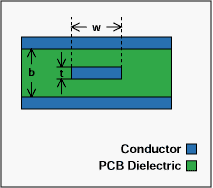

1.帶狀線:線走內板層,信號線是嵌在兩層導體之間的帶狀導線,它的電場分布都在兩個包它的導體(平面)之間,不會輻射能量出去,也不會受到外部的輻射干擾。但由于它的周圍全是電介(介電常數比1大),所以信號在里程中的傳輸速度比在表層中慢。

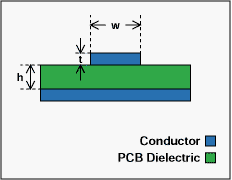

2. 微帶線:線走在板層表面, 如下圖,藍色部分是導體,綠色部分是PCB的絕緣電介質, 由于微帶線的一面裸露在空氣里面(可以向周圍形成信號輻射或受到周圍的輻射干擾),而另一面附在PCB的絕緣電介質上,所以它形成的電場一部分分布在空中,另一部分分布在PCB的絕緣介質中。但是微帶線中的信號傳輸速度要比帶狀線中的信號傳輸速度快,這是其突出的優點。

藍色部分是導體,綠色部分是PCB的絕緣電介質,上面的藍色小塊兒是microstrip line。

其中黃色部分是環氧有機材料。

3 其他知識點:

1.微帶線是一根帶狀導線(信號線).與地平面之間用一種電介質隔離開。如果線的厚度、寬度以及與地平面之間的距離是可控制的,則它的特性阻抗也是可以控制的。

2. 帶狀線是一條置于兩層導電平面之間的電介質中間的銅帶線。如果線的厚度和寬度、介質的介電常數以及兩層導電平面間的距離是可控制的,那么線的特性阻抗也是可控制的.

3. 單位長度微帶線的傳輸延遲時間,僅僅取決于介電常數,而與線的寬度或間隔無關

4. 微帶線速度塊,抗干擾能力弱,帶狀線速度慢些,抗干擾能力強些,因為微帶線一面是FR4(或者其他電介質)一面是空氣(介電常數低)因此速度很快,利于走對速度要求高的信號(例如差分線,通常為高速信號,同時抗干擾比較強)

5. 帶狀線兩邊都有電源或者地層,因此阻抗容易控制,同時屏蔽較好,但是信號速度慢些。

6. 通常同樣的介質條件微帶線的損耗小(線寬),帶狀線的損耗大(線細,有過孔)。

7. 當設計一個電路板時,首先要考慮的是需要多少布線層(routing layer)及電源平面(在可接受的成本價格內)。層數之決定在于功能規格、雜訊免疫力、信號分類、需布線之net、trace數目、阻抗之控制、VLSI元件密度、匯流排之布線,等等。適當使用microstrip及stripline方式以在PCB層面壓制射頻輻射。在PCB內之平面(Ground或VCC)是壓制PCB內Common-mode RF之重要方法之一,理由是這平面會降低高頻電源分布阻抗(power distribution impedance)。

8. Microstrip:指PCB之外層的trace,經一介電物質鄰接一整平面(solid plane). Microstrip方式提供PCB上之RF壓制,同時也可容許比sctripline較快之clock及邏輯訊號。此較快之clock及邏輯訊號是因為較小之耦合電容及較低之空載傳輸延遲。Microstrip的缺點是此PCB外部信號層會輻射RF能量引入環境,對非在此層之上下加入金屬屏蔽。

9. Stripline:信號層介于兩個solid planes (Voltage或Ground)之間。Stripline有達到較佳RF輻射防制,但只能用在較低之傳輸速度,因信號層介于兩個Solid planes之間,兩平面間會有電容性耦合,導致降低高速信號之邊緣速率(edge rate), Stripline之電容耦合效應在邊緣速率快于1ns之信號較為顯著,使用Stripline的主要效應是對內部trace之RF能量之完整屏蔽,因而對射頻有較佳之抑制能力。

要注意的是輻射仍然會從其他元件產生,雖然內部之trace可不令其產生輻射,其它之內部邊線(bond接線、元件腳、插座、內部連線能及其他類似者)仍會產生問題。隨著系統、元件、trace之阻抗,會存在阻抗不匹配(impedande mismatch)之問題,此不匹配之阻抗會使RF能量由內部trace耦合到其他電路或是自由空間(free space)。使元件之接腳電感最小(minimizing lead impedance)可降低輻射現象。

10. 微帶線和帶狀線的阻抗計算:

a.微帶線(microstrip) Z={87/[sqrt(Er+1.41)]}ln[5.98H/(0.8W+T)]

其中,W為線寬,T為走線的銅皮厚度,H為走線到參考平面的距離,Er是PCB板材質的介電常數(dielectricconstant)。此公式必須在0.1<(W/H)<2.0及1<(Er)<15的情況才能應用。

b.帶狀線(stripline) Z=[60/sqrt(Er)]ln{4H/[0.67π(T+0.8W)]}

其中,H為兩參考平面的距離,并且走線位于兩參考平面的中間。此公式必須在W/H<0.35及T/H<0.25的情況才能應用。